“Linux内核-网卡驱动移植”的版本间的差异

来自华清远见研发中心

(创建页面,内容为“==实验原理== STM32MP157A系列SoC集成一个千兆以太网媒体访问控制器,支持RMII和MII两种标准的PHY,FS-MP1A设备上外接了一个瑞昱的...”) |

(→实验原理) |

||

| 第5行: | 第5行: | ||

查看原理图得出RTL8211F数据管脚与STM32MP157A的管脚对应关系如下: | 查看原理图得出RTL8211F数据管脚与STM32MP157A的管脚对应关系如下: | ||

| + | |||

| + | {|class="wikitable" | ||

| + | |- | ||

| + | ! 原理图网络编号 !! 对应管脚 !! 管脚功能 !! 管脚功能码 | ||

| + | |- | ||

| + | | ETH_MDC | ||

| + | | PC1 | ||

| + | | ETH1_MDC | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_MDIO | ||

| + | | PA2 | ||

| + | | ETH1_MDIO | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TXD0 | ||

| + | | PG13 | ||

| + | | ETH1_*MII_ TXD0 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TXD1 | ||

| + | | PG14 | ||

| + | | ETH1_*MII_ TXD1 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TXD2 | ||

| + | | PC2 | ||

| + | | ETH1_*MII_ TXD2 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TXD3 | ||

| + | | PE2 | ||

| + | | ETH1_*MII_ TXD3 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TX_EN | ||

| + | | PB11 | ||

| + | | ETH1_*MII_ TX_EN | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_TX_CLK | ||

| + | | PG4 | ||

| + | | ETH1_*MII_ GTX_CLK | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RXD0 | ||

| + | | PC4 | ||

| + | | ETH1_*MII_ RXD0 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RXD1 | ||

| + | | PC5 | ||

| + | | ETH1_*MII_ RXD1 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RXD2 | ||

| + | | PB0 | ||

| + | | ETH1_*MII_ RXD2 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RXD3 | ||

| + | | PB1 | ||

| + | | ETH1_*MII_ RXD3 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RX_DV | ||

| + | | PA7 | ||

| + | | ETH1_*MII_RX _DV | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RX_CLK | ||

| + | | PA1 | ||

| + | | ETH1_*MII_RX _CLK | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_CLK125 | ||

| + | | PG5 | ||

| + | | ETH1_*MII_ CLK125 | ||

| + | | AF11 | ||

| + | |- | ||

| + | | ETH_RST | ||

| + | | PH2 | ||

| + | | ETH1_*MII_ CRS | ||

| + | | AF11 | ||

| + | |} | ||

| + | *网卡设备树节点<br> | ||

| + | |||

| + | 参考文档: | ||

| + | <pre><nowiki> | ||

| + | Documentation/devicetree/bindings/net/stm32-dwmac.txt | ||

| + | Documentation/devicetree/bindings/net/ethernet-controller.yaml | ||

| + | Documentation/devicetree/bindings/net/ethernet-phy.yaml | ||

| + | Documentation/devicetree/bindings/net/snps,dwmac.yam | ||

| + | </nowiki></pre> | ||

| + | 内核中ST对STM32MP15x系列芯片的设备树资源了做了定义,可参见: | ||

| + | arch/arm/boot/dts/stm32mp151.dtsi | ||

| + | stm32mp151中ethernet定义如下: | ||

| + | <pre><nowiki> | ||

| + | ethernet0: ethernet@5800a000 { | ||

| + | compatible = "st,stm32mp1-dwmac", "snps,dwmac-4.20a"; | ||

| + | reg = <0x5800a000 0x2000>; | ||

| + | reg-names = "stmmaceth"; | ||

| + | interrupts-extended = <&intc GIC_SPI 61 IRQ_TYPE_LEVEL_HIGH>, | ||

| + | <&exti 70 IRQ_TYPE_LEVEL_HIGH>; | ||

| + | interrupt-names = "macirq", | ||

| + | "eth_wake_irq"; | ||

| + | clock-names = "stmmaceth", | ||

| + | "mac-clk-tx", | ||

| + | "mac-clk-rx", | ||

| + | "ethstp"; | ||

| + | clocks = <&rcc ETHMAC>, | ||

| + | <&rcc ETHTX>, | ||

| + | <&rcc ETHRX>, | ||

| + | <&rcc ETHSTP>; | ||

| + | st,syscon = <&syscfg 0x4>; | ||

| + | snps,mixed-burst; | ||

| + | snps,pbl = <2>; | ||

| + | snps,en-tx-lpi-clockgating; | ||

| + | snps,axi-config = <&stmmac_axi_config_0>; | ||

| + | snps,tso; | ||

| + | power-domains = <&pd_core>; | ||

| + | status = "disabled"; | ||

| + | }; | ||

| + | </nowiki></pre> | ||

| + | 上述代码只对ethernet做了基本的初始化,并没有针对不同的硬件设计做适配,所以需结合硬件补全设备树节点信息。<br> | ||

| + | |||

| + | 对照内核文档目录下相关文档添加补充相关信息,亦可参考内核中其他设备树文件中相关描述,比如stm32mp15xx-dkx.dtsi关于ethernet的描述符合我们的要求,内容如下: | ||

| + | <pre><nowiki> | ||

| + | ðernet0 { | ||

| + | status = "okay"; | ||

| + | pinctrl-0 = <ðernet0_rgmii_pins_a>; | ||

| + | pinctrl-1 = <ðernet0_rgmii_pins_sleep_a>; | ||

| + | pinctrl-names = "default", "sleep"; | ||

| + | phy-mode = "rgmii-id"; | ||

| + | max-speed = <1000>; | ||

| + | phy-handle = <&phy0>; | ||

| + | |||

| + | mdio0 { | ||

| + | #address-cells = <1>; | ||

| + | #size-cells = <0>; | ||

| + | compatible = "snps,dwmac-mdio"; | ||

| + | phy0: ethernet-phy@0 { | ||

| + | reg = <0>; | ||

| + | }; | ||

| + | }; | ||

| + | }; | ||

| + | </nowiki></pre> | ||

| + | *管脚定义<br> | ||

| + | |||

| + | 在内核中STM32MP1默认管脚定义在文件arch/arm/dts/stm32mp15-pinctrl.dtsi中,查看文件中是否有需要的管脚定义:<br> | ||

| + | |||

| + | 查看后确认有ethernet的管脚定义,且与FS-MP1A硬件使用情况一致,定义如下: | ||

| + | <pre><nowiki> | ||

| + | ethernet0_rgmii_pins_a: rgmii-0 { | ||

| + | pins1 { | ||

| + | pinmux = <STM32_PINMUX('G', 5, AF11)>, /* ETH_RGMII_CLK125 */ | ||

| + | <STM32_PINMUX('G', 4, AF11)>, /* ETH_RGMII_GTX_CLK */ | ||

| + | <STM32_PINMUX('G', 13, AF11)>, /* ETH_RGMII_TXD0 */ | ||

| + | <STM32_PINMUX('G', 14, AF11)>, /* ETH_RGMII_TXD1 */ | ||

| + | <STM32_PINMUX('C', 2, AF11)>, /* ETH_RGMII_TXD2 */ | ||

| + | <STM32_PINMUX('E', 2, AF11)>, /* ETH_RGMII_TXD3 */ | ||

| + | <STM32_PINMUX('B', 11, AF11)>, /* ETH_RGMII_TX_CTL */ | ||

| + | <STM32_PINMUX('C', 1, AF11)>; /* ETH_MDC */ | ||

| + | bias-disable; | ||

| + | drive-push-pull; | ||

| + | slew-rate = <2>; | ||

| + | }; | ||

| + | pins2 { | ||

| + | pinmux = <STM32_PINMUX('A', 2, AF11)>; /* ETH_MDIO */ | ||

| + | bias-disable; | ||

| + | drive-push-pull; | ||

| + | slew-rate = <0>; | ||

| + | }; | ||

| + | pins3 { | ||

| + | pinmux = <STM32_PINMUX('C', 4, AF11)>, /* ETH_RGMII_RXD0 */ | ||

| + | <STM32_PINMUX('C', 5, AF11)>, /* ETH_RGMII_RXD1 */ | ||

| + | <STM32_PINMUX('B', 0, AF11)>, /* ETH_RGMII_RXD2 */ | ||

| + | <STM32_PINMUX('B', 1, AF11)>, /* ETH_RGMII_RXD3 */ | ||

| + | <STM32_PINMUX('A', 1, AF11)>, /* ETH_RGMII_RX_CLK */ | ||

| + | <STM32_PINMUX('A', 7, AF11)>; /* ETH_RGMII_RX_CTL */ | ||

| + | bias-disable; | ||

| + | }; | ||

| + | }; | ||

| + | |||

| + | ethernet0_rgmii_pins_sleep_a: rgmii-sleep-0 { | ||

| + | pins1 { | ||

| + | pinmux = <STM32_PINMUX('G', 5, ANALOG)>, /* ETH_RGMII_CLK125 */ | ||

| + | <STM32_PINMUX('G', 4, ANALOG)>, /* ETH_RGMII_GTX_CLK */ | ||

| + | <STM32_PINMUX('G', 13, ANALOG)>, /* ETH_RGMII_TXD0 */ | ||

| + | <STM32_PINMUX('G', 14, ANALOG)>, /* ETH_RGMII_TXD1 */ | ||

| + | <STM32_PINMUX('C', 2, ANALOG)>, /* ETH_RGMII_TXD2 */ | ||

| + | <STM32_PINMUX('E', 2, ANALOG)>, /* ETH_RGMII_TXD3 */ | ||

| + | <STM32_PINMUX('B', 11, ANALOG)>, /* ETH_RGMII_TX_CTL */ | ||

| + | <STM32_PINMUX('A', 2, ANALOG)>, /* ETH_MDIO */ | ||

| + | <STM32_PINMUX('C', 1, ANALOG)>, /* ETH_MDC */ | ||

| + | <STM32_PINMUX('C', 4, ANALOG)>, /* ETH_RGMII_RXD0 */ | ||

| + | <STM32_PINMUX('C', 5, ANALOG)>, /* ETH_RGMII_RXD1 */ | ||

| + | <STM32_PINMUX('B', 0, ANALOG)>, /* ETH_RGMII_RXD2 */ | ||

| + | <STM32_PINMUX('B', 1, ANALOG)>, /* ETH_RGMII_RXD3 */ | ||

| + | <STM32_PINMUX('A', 1, ANALOG)>, /* ETH_RGMII_RX_CLK */ | ||

| + | <STM32_PINMUX('A', 7, ANALOG)>; /* ETH_RGMII_RX_CTL */ | ||

| + | }; | ||

| + | }; | ||

| + | </nowiki></pre> | ||

==实验目的== | ==实验目的== | ||

2020年7月28日 (二) 08:48的版本

实验原理

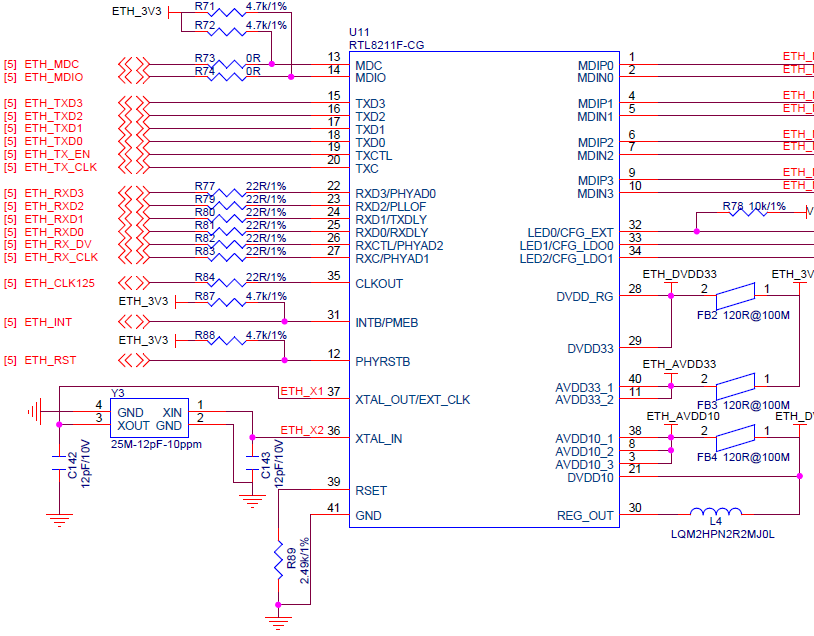

STM32MP157A系列SoC集成一个千兆以太网媒体访问控制器,支持RMII和MII两种标准的PHY,FS-MP1A设备上外接了一个瑞昱的千兆以太网PHY芯片RTL8211F,原理图如下:

查看原理图得出RTL8211F数据管脚与STM32MP157A的管脚对应关系如下:

| 原理图网络编号 | 对应管脚 | 管脚功能 | 管脚功能码 |

|---|---|---|---|

| ETH_MDC | PC1 | ETH1_MDC | AF11 |

| ETH_MDIO | PA2 | ETH1_MDIO | AF11 |

| ETH_TXD0 | PG13 | ETH1_*MII_ TXD0 | AF11 |

| ETH_TXD1 | PG14 | ETH1_*MII_ TXD1 | AF11 |

| ETH_TXD2 | PC2 | ETH1_*MII_ TXD2 | AF11 |

| ETH_TXD3 | PE2 | ETH1_*MII_ TXD3 | AF11 |

| ETH_TX_EN | PB11 | ETH1_*MII_ TX_EN | AF11 |

| ETH_TX_CLK | PG4 | ETH1_*MII_ GTX_CLK | AF11 |

| ETH_RXD0 | PC4 | ETH1_*MII_ RXD0 | AF11 |

| ETH_RXD1 | PC5 | ETH1_*MII_ RXD1 | AF11 |

| ETH_RXD2 | PB0 | ETH1_*MII_ RXD2 | AF11 |

| ETH_RXD3 | PB1 | ETH1_*MII_ RXD3 | AF11 |

| ETH_RX_DV | PA7 | ETH1_*MII_RX _DV | AF11 |

| ETH_RX_CLK | PA1 | ETH1_*MII_RX _CLK | AF11 |

| ETH_CLK125 | PG5 | ETH1_*MII_ CLK125 | AF11 |

| ETH_RST | PH2 | ETH1_*MII_ CRS | AF11 |

- 网卡设备树节点

参考文档:

Documentation/devicetree/bindings/net/stm32-dwmac.txt Documentation/devicetree/bindings/net/ethernet-controller.yaml Documentation/devicetree/bindings/net/ethernet-phy.yaml Documentation/devicetree/bindings/net/snps,dwmac.yam

内核中ST对STM32MP15x系列芯片的设备树资源了做了定义,可参见:

arch/arm/boot/dts/stm32mp151.dtsi

stm32mp151中ethernet定义如下:

ethernet0: ethernet@5800a000 {

compatible = "st,stm32mp1-dwmac", "snps,dwmac-4.20a";

reg = <0x5800a000 0x2000>;

reg-names = "stmmaceth";

interrupts-extended = <&intc GIC_SPI 61 IRQ_TYPE_LEVEL_HIGH>,

<&exti 70 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "macirq",

"eth_wake_irq";

clock-names = "stmmaceth",

"mac-clk-tx",

"mac-clk-rx",

"ethstp";

clocks = <&rcc ETHMAC>,

<&rcc ETHTX>,

<&rcc ETHRX>,

<&rcc ETHSTP>;

st,syscon = <&syscfg 0x4>;

snps,mixed-burst;

snps,pbl = <2>;

snps,en-tx-lpi-clockgating;

snps,axi-config = <&stmmac_axi_config_0>;

snps,tso;

power-domains = <&pd_core>;

status = "disabled";

};

上述代码只对ethernet做了基本的初始化,并没有针对不同的硬件设计做适配,所以需结合硬件补全设备树节点信息。

对照内核文档目录下相关文档添加补充相关信息,亦可参考内核中其他设备树文件中相关描述,比如stm32mp15xx-dkx.dtsi关于ethernet的描述符合我们的要求,内容如下:

ðernet0 {

status = "okay";

pinctrl-0 = <ðernet0_rgmii_pins_a>;

pinctrl-1 = <ðernet0_rgmii_pins_sleep_a>;

pinctrl-names = "default", "sleep";

phy-mode = "rgmii-id";

max-speed = <1000>;

phy-handle = <&phy0>;

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "snps,dwmac-mdio";

phy0: ethernet-phy@0 {

reg = <0>;

};

};

};

- 管脚定义

在内核中STM32MP1默认管脚定义在文件arch/arm/dts/stm32mp15-pinctrl.dtsi中,查看文件中是否有需要的管脚定义:

查看后确认有ethernet的管脚定义,且与FS-MP1A硬件使用情况一致,定义如下:

ethernet0_rgmii_pins_a: rgmii-0 {

pins1 {

pinmux = <STM32_PINMUX('G', 5, AF11)>, /* ETH_RGMII_CLK125 */

<STM32_PINMUX('G', 4, AF11)>, /* ETH_RGMII_GTX_CLK */

<STM32_PINMUX('G', 13, AF11)>, /* ETH_RGMII_TXD0 */

<STM32_PINMUX('G', 14, AF11)>, /* ETH_RGMII_TXD1 */

<STM32_PINMUX('C', 2, AF11)>, /* ETH_RGMII_TXD2 */

<STM32_PINMUX('E', 2, AF11)>, /* ETH_RGMII_TXD3 */

<STM32_PINMUX('B', 11, AF11)>, /* ETH_RGMII_TX_CTL */

<STM32_PINMUX('C', 1, AF11)>; /* ETH_MDC */

bias-disable;

drive-push-pull;

slew-rate = <2>;

};

pins2 {

pinmux = <STM32_PINMUX('A', 2, AF11)>; /* ETH_MDIO */

bias-disable;

drive-push-pull;

slew-rate = <0>;

};

pins3 {

pinmux = <STM32_PINMUX('C', 4, AF11)>, /* ETH_RGMII_RXD0 */

<STM32_PINMUX('C', 5, AF11)>, /* ETH_RGMII_RXD1 */

<STM32_PINMUX('B', 0, AF11)>, /* ETH_RGMII_RXD2 */

<STM32_PINMUX('B', 1, AF11)>, /* ETH_RGMII_RXD3 */

<STM32_PINMUX('A', 1, AF11)>, /* ETH_RGMII_RX_CLK */

<STM32_PINMUX('A', 7, AF11)>; /* ETH_RGMII_RX_CTL */

bias-disable;

};

};

ethernet0_rgmii_pins_sleep_a: rgmii-sleep-0 {

pins1 {

pinmux = <STM32_PINMUX('G', 5, ANALOG)>, /* ETH_RGMII_CLK125 */

<STM32_PINMUX('G', 4, ANALOG)>, /* ETH_RGMII_GTX_CLK */

<STM32_PINMUX('G', 13, ANALOG)>, /* ETH_RGMII_TXD0 */

<STM32_PINMUX('G', 14, ANALOG)>, /* ETH_RGMII_TXD1 */

<STM32_PINMUX('C', 2, ANALOG)>, /* ETH_RGMII_TXD2 */

<STM32_PINMUX('E', 2, ANALOG)>, /* ETH_RGMII_TXD3 */

<STM32_PINMUX('B', 11, ANALOG)>, /* ETH_RGMII_TX_CTL */

<STM32_PINMUX('A', 2, ANALOG)>, /* ETH_MDIO */

<STM32_PINMUX('C', 1, ANALOG)>, /* ETH_MDC */

<STM32_PINMUX('C', 4, ANALOG)>, /* ETH_RGMII_RXD0 */

<STM32_PINMUX('C', 5, ANALOG)>, /* ETH_RGMII_RXD1 */

<STM32_PINMUX('B', 0, ANALOG)>, /* ETH_RGMII_RXD2 */

<STM32_PINMUX('B', 1, ANALOG)>, /* ETH_RGMII_RXD3 */

<STM32_PINMUX('A', 1, ANALOG)>, /* ETH_RGMII_RX_CLK */

<STM32_PINMUX('A', 7, ANALOG)>; /* ETH_RGMII_RX_CTL */

};

};

实验目的

熟悉基于Linux操作系统下的网卡驱动移植配置过程。

实验平台

华清远见开发环境,FS-MP1A平台;

实验步骤

- 添加网卡设备树配置。

修改arch/arm/dts/stm32mp15xx-fsmp1x.dts文件

在文件末尾添加如下内容:

ðernet0 {

status = "okay";

pinctrl-0 = <ðernet0_rgmii_pins_a>;

pinctrl-1 = <ðernet0_rgmii_pins_sleep_a>;

pinctrl-names = "default", "sleep";

phy-mode = "rgmii-id";

max-speed = <1000>;

phy-handle = <&phy0>;

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "snps,dwmac-mdio";

phy0: ethernet-phy@0 {

reg = <0>;

};

};

};

- 配置内核

由于内核源码默认配置以及支持网卡,本节列出主要选项,如下:

linux@ubuntu:$ make menuconfig Device Drivers ---> [*] Network device support ---> [*] Ethernet driver support ---> <*> STMicroelectronics Multi-Gigabit Ethernet driver <*> STMMAC Platform bus support <*> Support for snps,dwc-qos-ethernet.txt DT binding. <*> Generic driver for DWMAC <*> STM32 DWMAC support

- 编译内核及设备树:

linux@ubuntu:$ make -j4 uImage dtbs LOADADDR=0xC2000040

- 重启测试

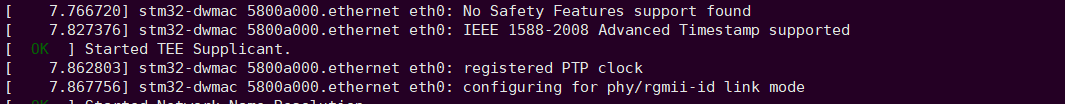

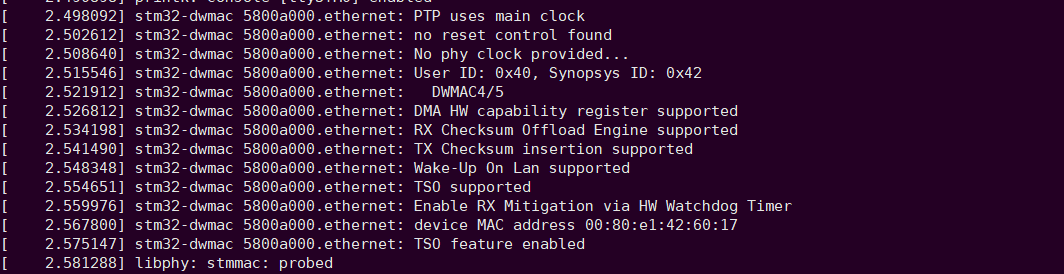

将编译好的设备树和内核镜像拷贝到/tftpboot目录下,通过tftp引导内核,重启设备后可以看到如下启动信息:

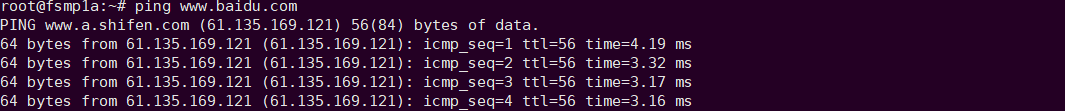

通过Ping 测试网卡

linux@fsmp1a:$ ping www.baidu.com

如果设备不能接入以太网,可以ping主机